- TinyEngine thay interpreter-based execution bằng code generation, giảm peak SRAM 3.4x và tăng tốc inference 1.7-3.3x so với TF-Lite Micro và CMSIS-NN.

- Loop reordering đơn thuần cho 12x speedup mà không cần đổi hardware - chỉ thay thứ tự vòng lặp.

- MCUNet đạt 70.7% ImageNet top-1 accuracy trên MCU giá $5, lần đầu tiên vượt ngưỡng 70% trên vi điều khiển thương mại.

- MIT License, open-source, chạy trên STM32 và OpenMV Cam H7.

TL;DR

TinyEngine là inference engine của framework MCUNet (MIT HAN Lab) - được thiết kế để chạy deep learning trên vi điều khiển (MCU) chỉ có vài trăm KB RAM. Thay vì dùng interpreter như TF-Lite Micro hay CMSIS-NN, TinyEngine sinh code C/C++ đặc thù cho từng model tại compile time, loại bỏ toàn bộ overhead runtime.

Kết quả: inference nhanh hơn 1.1-18.6x, peak memory giảm 1.3-3.6x, binary size nhỏ hơn 4.5-5x so với các thư viện cùng loại. MCUNet kết hợp TinyEngine đạt 70.7% ImageNet top-1 trên MCU thương mại giá $5 - lần đầu tiên vượt 70% trên hardware loại này.

AI trên vi điều khiển: bài toán khó

MCU như STM32F746 chỉ có 320KB SRAM và 1MB Flash - nhỏ hơn GPU đến 50.000 lần. Deploying deep learning trên những thiết bị này đòi hỏi tư duy khác hoàn toàn so với GPU hay mobile:

- SRAM nhỏ - activation buffer tạm thời cực kỳ nguy hiểm

- Flash hạn chế - binary size phải tối thiểu

- Không có OS, không có DRAM - bare-metal hoàn toàn

- Chi phí memory movement cao hơn arithmetic

Các thư viện interpreter-based như TF-Lite Micro và CMSIS-NN tiêu tốn đến 65% peak memory chỉ để lưu meta-information của model, và cộng thêm 22% latency từ runtime interpretation. TinyEngine giải quyết bằng cách compile trực tiếp.

Kỹ thuật song song hóa - xa hơn CUDA

Lecture 11 của khóa EfficientML (MIT 6.5940) tập trung vào 4 kỹ thuật song song hóa cốt lõi, áp dụng được cho cả MCU lẫn LLM deployment:

Loop Reordering - thay đổi thứ tự vòng lặp để cải thiện cache locality. Với matrix multiplication, đổi từ i-j-k sang i-k-j giúp processor truy cập memory tuần tự hơn. Kết quả: 12x speedup (24.000ms xuống dưới 2.000ms) trên Intel Z4114, không thay bất kỳ hardware nào.

Loop Tiling - chia computation thành các block nhỏ vừa cache. Khi matrix lớn hơn cache, data bị evict trước khi được dùng lại. Tiling giữ data trong cache đến khi dùng xong. Chiến lược 6-loop tiling đạt 20x speedup (24.000ms xuống 1.200ms) - gần gấp đôi so với chỉ reordering.

Loop Unrolling - xử lý nhiều iterations per loop để giảm overhead (index arithmetic, branch checks, jump instructions). TinyEngine chuyên biệt hóa: 9 code segments cho kernel 3x3, 25 segments cho kernel 5x5, loại bỏ branch prediction overhead. Trade-off: tăng binary size - quan trọng khi Flash hạn chế.

SIMD (Single Instruction, Multiple Data) - áp dụng một instruction cho nhiều giá trị đồng thời. ARM NEON và x86 SSE cho phép xử lý nhiều float trong một phép tính. SIMD không chỉ tăng tốc độ mà còn cải thiện energy efficiency - quan trọng cho always-on IoT devices.

Tối ưu bộ nhớ đặc thù cho inference

Ngoài song song hóa, TinyEngine giải quyết bài toán bộ nhớ bằng 3 kỹ thuật chính:

In-Place Depth-Wise Convolution: Convolution thông thường cần 2 buffer (input + output) - tổng 2 x C x H x W. TinyEngine ghi đè output lên input buffer ngay khi safe, giảm xuống còn N+1. Kết quả: 1.6x giảm memory thực đo được.

Patch-Based Inference: Thay vì xử lý toàn bộ feature map cùng lúc, chỉ xử lý một vùng nhỏ. Với MobileNetV2, kỹ thuật này giảm peak memory 8x - đủ để fit model lớn hơn trong cùng ngân sách bộ nhớ.

Model-Adaptive Memory Scheduling: Thay vì tối ưu từng layer riêng lẻ (như TF-Lite Micro), TinyEngine phân tích toàn bộ network topology để tính M - maximum memory cần thiết để fit một column transformed inputs qua tất cả layers. Từ M này, loop tiling size được điều chỉnh per-layer để tối đa data reuse. Kỹ thuật này cải thiện inference efficiency thêm 13%.

Số liệu so sánh

| Metric | TF-Lite Micro | CMSIS-NN | TinyEngine |

|---|---|---|---|

| mcunet-in0 latency | 586ms | 51ms | 25ms |

| mcunet-in0 SRAM | 161kB | 161kB | 49kB |

| mcunet-in4 latency | OOM | OOM | 463ms |

| Binary size | 1x (base) | ~1x | 4.5-5x nho hon |

| ImageNet top-1 (MCU) | ~69.8% | 70.7% | |

Dòng mcunet-in4 minh họa rõ nhất lợi thế: TF-Lite Micro và CMSIS-NN đều Out-Of-Memory, trong khi TinyEngine vẫn chạy được nhờ memory scheduling thông minh hơn.

Đánh đổi cần biết

- Model-specific compilation: đổi kiến trúc model phải recompile lại - mất tính linh hoạt của interpreter

- Loop unrolling vs Flash: tốc độ tăng nhưng binary size tăng theo - phải cân nhắc với Flash budget

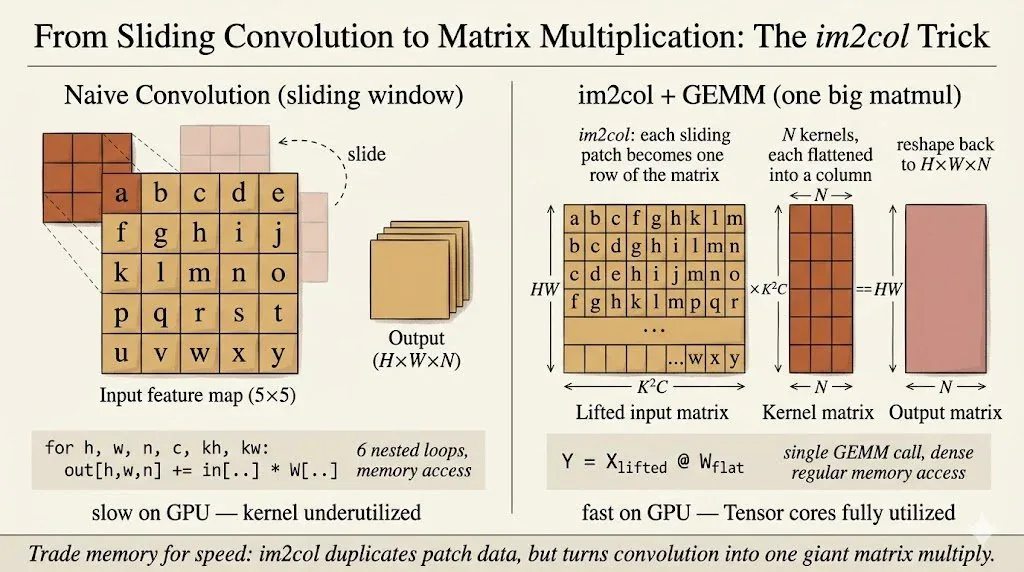

- Im2col temp buffer: vẫn cần buffer tạm để duplicate overlapping pixels - có thể gây OOM trên MCU nhỏ nhất

- ARM-focused: tối ưu nhất trên Cortex-M4/M7, chưa có broad support cho các nền tảng khác

Ai nên dùng - và tiếp theo là gì?

TinyEngine phù hợp nhất cho: AIoT developers cần deploy vision/audio model trên MCU <512KB SRAM; nghiên cứu về TinyML; và bất kỳ ai muốn hiểu sâu về hardware-software co-design.

Roadmap của MIT HAN Lab sau TinyEngine: MCUNetV3 (NeurIPS 2022) đã enable on-device training dưới 256KB - model học trực tiếp trên MCU mà không cần cloud. Hướng tiếp theo là mixed-precision quantization và áp dụng cùng loop optimization principles cho LLM deployment - khóa EfficientML 2023 đã dùng các kỹ thuật này để deploy LLaMA 2 7B trên laptop.

Nguồn: Efficient AI Lecture 11 - ickma.dev, mit-han-lab/tinyengine, MCUNet paper (NeurIPS 2020).